# JN Semiconductor®

To kara more about Old Semiconductor, please visit our website at

Please note. As part of the Fairchild Semiconductor integration, some of the Fairchild orderable part numbers will need to change in order to meet ON Semiconductor's system requirements. Since the ON Semiconductor product management systems do not have the ability to manage part nomenclature that utilizes an underscore (\_), the underscore (\_) in the Fairchild part numbers will be changed to a dash (-). This document may contain device numbers with an underscore (\_). Please check the ON Semiconductor website to verify the updated device numbers. The most current and up-to-date ordering information can be found at <a href="www.onsemi.com">www.onsemi.com</a>. Please email any questions regarding the system integration to Fairchild <a href="guestions@onsemi.com">questions@onsemi.com</a>.

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any EDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officer

February 2016

### FSBB15CH60C

## Motion SPM® 3 Series

#### **Features**

- UL Certified No. E209204 (UL1557)

- 600 V 15 A 3-Phase IGBT Inverter with Integral Gate Drivers and Protection

- · Low-Loss, Short-Circuit Rated IGBTs

- Very Low Thermal Resistance Using Al<sub>2</sub>O<sub>3</sub> DBC Substrate

- Built-in Bootstrap Diodes and Dedicated Vs Pins Simplify PCB Layout

- Separate Open-Emitter Pins from Low-Side IGBTs for Three-Phase Current Sensing

- · Single-Grounded Power Supply

- Isolation Rating: 2500 V<sub>rms</sub> / min.

### **Applications**

Motion Control - Home Applian / Indu, ial. ntor

### Related Resourc

• AN-9044 - I tion CDM les L'sers Guide

### **General Description**

FSBB15CH60C is an advanced Motion SPM® 3 module providing a fully-featured, high-performance inverter output stage for AC Induction, BLDC, and PMSM motors. These modules integrate optiming gate drive of the built-in IGBTs to minimize E' and Ichres, while also providing multiple on-module promotion in turnes including under-voltage lock as, over-concentration of turnes including under-voltage lock as, over-concentration in turnes including under-voltage lock as, over-concentration of the incoming logic-level gas input to the ingh-voltage, high-current drive signed as input to properly drive the module's integrated by properly drive the module's integrated by phase to support the widest variety of control of goritimas.

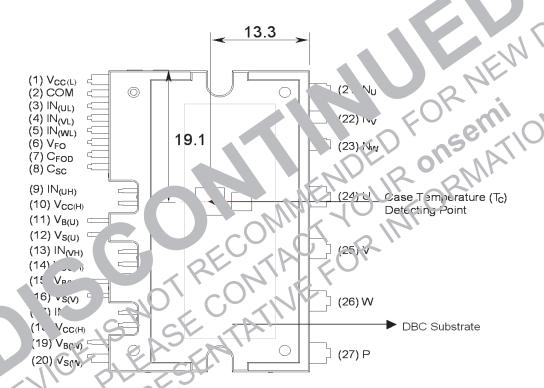

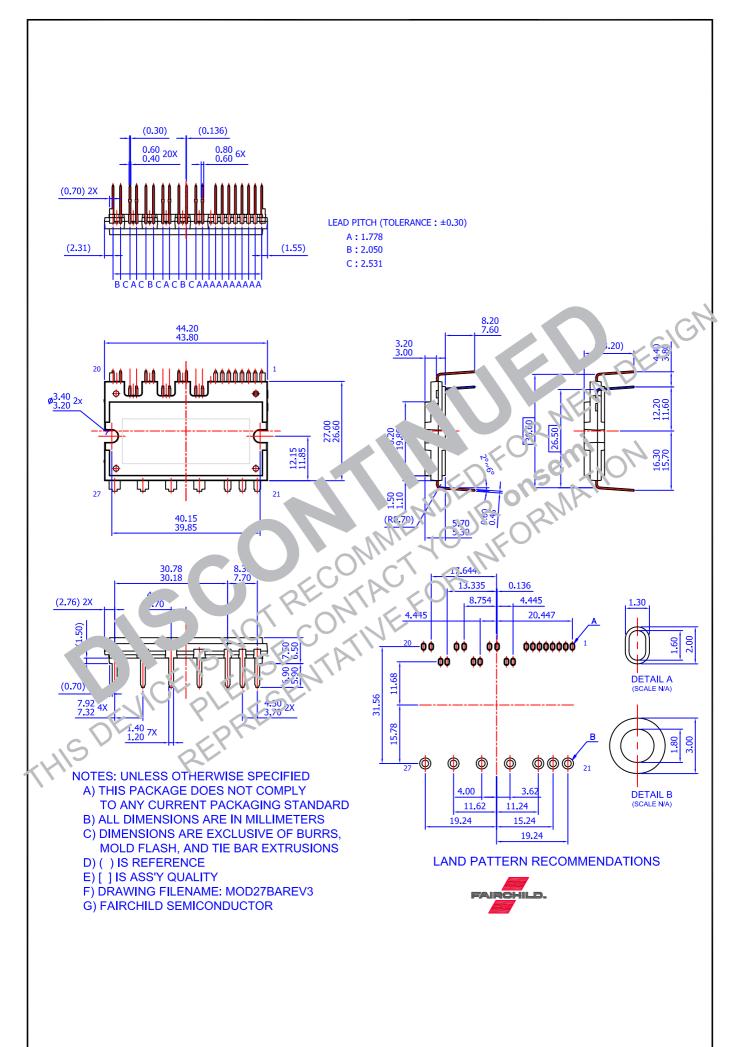

Figure 1. Package Overview

### **Package Marking and Ordering Information**

| Device      | Device Marking | Package   | Package Packing Type |    |

|-------------|----------------|-----------|----------------------|----|

| FSBB15CH60C | FSBB15CH60C    | SPMCC-027 | Rail                 | 10 |

### **Integrated Power Functions**

• 600 V - 15 A IGBT inverter for three-phase DC / AC power conversion (please refer to Figure 3)

### **Integrated Drive, Protection, and System Control Functions**

- For inverter high-side IGBTs: gate drive circuit, high-voltage isolated high-speed level shifting

control circuit Under-Voltage Lock-Out Protection (UVLO)

Note: Available bootstrap circuit example is given in Figures 12 and 13.

- For inverter low-side IGBTs: gate drive circuit, Short-Circuit Protection (SCP)

control supply circuit Under-Voltage Lock-Out Protection (UVLO)

- · Fault signaling: corresponding to UVLO (low-side supply) and SC faults

- Input interface: active-HIGH interface, works with 3.3 / 5 V logic, Schmitt-trigger input

### **Pin Configuration**

Figure 2. Top View

### **Pin Descriptions**

| Pin Number | Pin Name           | Pin Description                                                       |

|------------|--------------------|-----------------------------------------------------------------------|

| 1          | V <sub>CC(L)</sub> | Low-Side Common Bias Voltage for IC and IGBTs Driving                 |

| 2          | COM                | Common Supply Ground                                                  |

| 3          | IN <sub>(UL)</sub> | Signal Input for Low-Side U-Phase                                     |

| 4          | IN <sub>(VL)</sub> | Signal Input for Low-Side V-Phase                                     |

| 5          | IN <sub>(WL)</sub> | Signal Input for Low-Side W-Phase                                     |

| 6          | V <sub>FO</sub>    | Fault Output                                                          |

| 7          | C <sub>FOD</sub>   | Capacitor for Fault Output Duration Selection                         |

| 8          | C <sub>SC</sub>    | Capacitor (Low-Pass Filter) for Short-Circuit Current Detection Input |

| 9          | IN <sub>(UH)</sub> | Signal Input for High-Side U-Phase                                    |

| 10         | V <sub>CC(H)</sub> | High-Side Common Bias Voltage for IC and IGBTs Driving                |

| 11         | V <sub>B(U)</sub>  | High-Side Bias Voltage for U-Phase IGBT Driving                       |

| 12         | V <sub>S(U)</sub>  | High-Side Bias Voltage Ground for U-Phase IGBT. 'ving                 |

| 13         | IN <sub>(VH)</sub> | Signal Input for High-Side V-Phase                                    |

| 14         | V <sub>CC(H)</sub> | High-Side Common Bias Voltage for IC & 1 IG. 3 Drivi                  |

| 15         | V <sub>B(V)</sub>  | High-Side Bias Voltage for V-Pha.                                     |

| 16         | V <sub>S(V)</sub>  | High-Side Bias Voltage Groun. for Nohaso T Driving                    |

| 17         | IN <sub>(WH)</sub> | Signal Input for High W-Ph                                            |

| 18         | V <sub>CC(H)</sub> | High-Side Com on Bias Itage for C and GDTs Driving                    |

| 19         | $V_{B(W)}$         | High-Sid Signary Vo. ge for V. Phase IGBT Driving                     |

| 20         | V <sub>S(W)</sub>  | High Cide L is v. Ground for W-Phase IGB Liviving                     |

| 21         | N <sub>U</sub>     | uegativ√ C k Input for U∵Phase                                        |

| 22         | N.                 | 'egative C-Link Input in V-Phase                                      |

| 23         | W                  | N. DC-Link Input for W-Phase                                          |

| 24         |                    | Output for 1) Phase                                                   |

| 25         | V                  | Output for V-Phase                                                    |

| 26         | W                  | Ou put for W-Phase                                                    |

|            | P                  | Positir e DC-Link Input                                               |

| SDEVIC     | 1/3/               | ASTATIA                                                               |

| 11(        |                    | CE                                                                    |

| ///        | PV                 |                                                                       |

| OF         | · · ·              |                                                                       |

| SY         |                    | <b>&gt;</b>                                                           |

|            | KV                 |                                                                       |

|            | -                  |                                                                       |

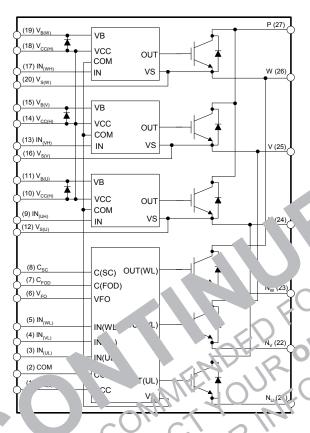

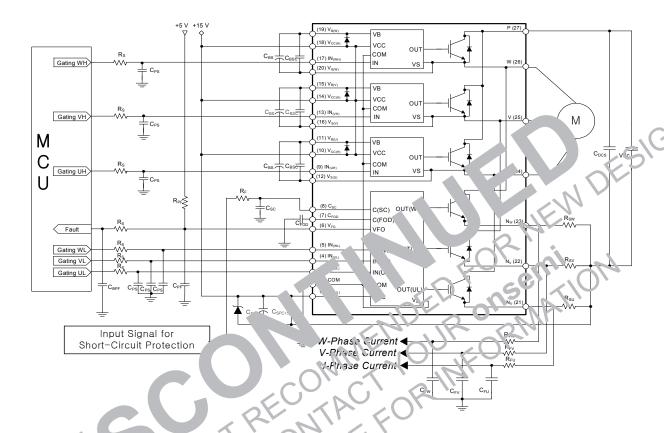

### **Internal Equivalent Circuit and Input/Output Pins**

### rigure 3 Internal Block Diagram

#### 1st Notes:

- 1. Inverter low-side is mposed of thre eewherling divides for each ICBT and one control IC. It has gate drive and protection functions.

- 2. Inverter pov side four inverter PC-link input terminals and three inverter disput terminals.

- 3. Inverter high-s is composed inree IGBTs, freewheeling dioces, and arree drive ICs for each IGBT.

### **Absolute Maximum Ratings** (T<sub>J</sub> = 25°C, unless otherwise specified.)

#### **Inverter Part**

| Symbol                 | Parameter                          | Conditions                                                            | Rating | Unit |

|------------------------|------------------------------------|-----------------------------------------------------------------------|--------|------|

| $V_{PN}$               | Supply Voltage                     | Applied between P - N <sub>U</sub> , N <sub>V</sub> , N <sub>W</sub>  | 450    | V    |

| V <sub>PN(Surge)</sub> | Supply Voltage (Surge)             | Applied between P - N <sub>U</sub> , N <sub>V</sub> , N <sub>W</sub>  | 500    | V    |

| V <sub>CES</sub>       | Collector - Emitter Voltage        |                                                                       | 600    | V    |

| ± I <sub>C</sub>       | Each IGBT Collector Current        | $T_{C} = 25^{\circ}C, T_{J} \le 150^{\circ}C$                         | 15     | Α    |

| ± I <sub>CP</sub>      | Each IGBT Collector Current (Peak) | $T_C = 25^{\circ}C$ , $T_J \le 150^{\circ}C$ , Under 1 ms Pulse Width | 30     | Α    |

| P <sub>C</sub>         | Collector Dissipation              | T <sub>C</sub> = 25°C per Chip                                        | 55     | W    |

| T <sub>J</sub>         | Operating Junction Temperature     | (2nd Note 1)                                                          | 40 150 | °C   |

#### 2nd Notes

#### **Control Part**

| Symbol          | Parameter                      | Condit. 1s                                                      | Kating                       | Unit |

|-----------------|--------------------------------|-----------------------------------------------------------------|------------------------------|------|

| V <sub>CC</sub> | Control Supply Voltage         | Applied between V <sub>CC</sub> , V <sub>C</sub> , - C .M       | 20                           | V    |

| V <sub>BS</sub> | High-Side Control Bias Voltage | Applied botwe $V_{B(N)}$ , $V_{B(N)}$ , $V_{B(N)}$ , $V_{B(N)}$ | 20                           | V    |

| V <sub>IN</sub> | Input Signal Voltage           | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$           | -3 5 ~ V <sub>CC</sub> · 0.5 | V    |

| $V_{FO}$        | Fault Output Supply Voltage    | Applied atween VEO - COM                                        | -C.3 v <sub>CC</sub> + 0.3   | V    |

| I <sub>FO</sub> | Fault Output Current           | h nk Current at V <sub>i=O</sub> pin                            | 5                            | mA   |

| V <sub>SC</sub> | Current-Sensing Input stage    | Applied between C <sub>SC</sub> - COM                           | -0.3 ~ V <sub>CC</sub> + 0.3 | V    |

### Bootstrap Diode Part

| Symbol           | Parai eter Conditions                                                                       | Rating    | Unit |

|------------------|---------------------------------------------------------------------------------------------|-----------|------|

| V <sub>RRM</sub> | aximum Re,                                                                                  | 600       | ٧    |

| l <sub>F</sub>   | For and Corent $\Gamma_C = 25^{\circ}  \text{C}, \Gamma_2 \leq 150^{\circ} \text{C}$        | 0.5       | Α    |

|                  | For urrent (1.23's) $T_C = 25^{\circ}C$ , $T_J \le 150^{\circ}C$ Under 1 ms Pulse $V'$ idth | 2.0       | Α    |

| T <sub>J</sub>   | Operating Junction Tennesclure                                                              | -40 ~ 150 | °C   |

### Total System

| Symbol           | Parameter                                                                   | Conditions                                                                     | Rating    | Unit             |

|------------------|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------|-----------|------------------|

| N(PROT)          | Self-Protection Supply Voltage Limit (Short-C.rc. if Protection Capability) | $V_{CC}$ = $V_{BS}$ = 13.5 ~ 16.5 V<br>$T_{J}$ = 150°C, Non-Repetitive, < 2 μs | 400       | V                |

| T <sub>C</sub>   | Module Case Operation Temperature                                           | -40°C ≤ T <sub>J</sub> ≤ 150°C, See Figure 2                                   | -40 ~ 125 | °C               |

| T <sub>STG</sub> | Storage Temperature                                                         |                                                                                | -40 ~ 125 | °C               |

| V <sub>ISO</sub> | Isolation Voltage                                                           | 60 Hz, Sinusoidal, AC 1 Minute, Connect Pins to Heat Sink Plate                | 2500      | V <sub>rms</sub> |

#### **Thermal Resistance**

| Symbol                | Parameter                           | Conditions                            | Min. | Тур. | Max. | Unit   |

|-----------------------|-------------------------------------|---------------------------------------|------|------|------|--------|

| R <sub>th(j-c)Q</sub> | Junction to Case Thermal Resistance | Inverter IGBT part (per 1 / 6 module) | -    | -    | 2.27 | °C / W |

| R <sub>th(j-c)F</sub> |                                     | Inverter FWDi part (per 1 / 6 module) | -    | -    | 3.0  | °C/W   |

#### 2nd Notes:

<sup>1.</sup> The maximum junction temperature rating of the power chips integrated within the Motion SPM $^{\circledR}$  3 product is 150 $^{\circ}$ C (at T<sub>C</sub>  $\leq$   $^{\prime}$  C)

<sup>2.</sup> For the measurement point of case temperature ( $T_{\mathbb{C}}$ ), please refer to Figure 2.

### **Electrical Characteristics** (T<sub>J</sub> = 25°C, unless otherwise specified.)

#### **Inverter Part**

| S                    | ymbol               | Parameter                              | Condi                                                                                               | tions                                        | Min.     | Тур. | Max.  | Unit |

|----------------------|---------------------|----------------------------------------|-----------------------------------------------------------------------------------------------------|----------------------------------------------|----------|------|-------|------|

| V <sub>CE(SAT)</sub> |                     | Collector - Emitter Saturation Voltage | V <sub>CC</sub> = V <sub>BS</sub> = 15 V<br>V <sub>IN</sub> = 5 V                                   | I <sub>C</sub> = 15 A, T <sub>J</sub> = 25°C | -        | -    | 2.0   | V    |

|                      | V <sub>F</sub>      | FWDi Forward Voltage                   | V <sub>IN</sub> = 0 V                                                                               | I <sub>F</sub> = 15 A, T <sub>J</sub> = 25°C | -        | -    | 2.2   | V    |

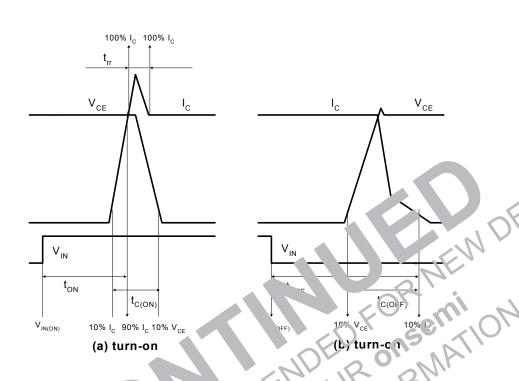

| HS                   | t <sub>ON</sub>     | Switching Times                        | V <sub>PN</sub> = 300 V, V <sub>CC</sub> = V <sub>B</sub>                                           | <sub>S</sub> = 15 V                          | -        | 0.80 | -     | μs   |

|                      | t <sub>C(ON)</sub>  |                                        | $  I_C = 15 A$<br>$  V_{IN} = 0 V \leftrightarrow 5 V$ , Inducti                                    | ve Load                                      | -        | 0.20 | -     | μs   |

|                      | t <sub>OFF</sub>    |                                        | (2nd Note 3)                                                                                        | ve Load                                      | -        | 0.40 | -     | μs   |

|                      | t <sub>C(OFF)</sub> |                                        |                                                                                                     |                                              | -        | 0.10 | -     | μs   |

|                      | t <sub>rr</sub>     |                                        |                                                                                                     |                                              | -        | -    | -     | μs   |

| LS                   | t <sub>ON</sub>     |                                        | V <sub>PN</sub> = 300 V, V <sub>CC</sub> = V <sub>B</sub>                                           | <sub>S</sub> = 15 V                          | -        | 50   |       | μs   |

|                      | t <sub>C(ON)</sub>  |                                        | $  I_C = 15 \text{ A}  $<br>$  V_{IN} = 0 \text{ V} \leftrightarrow 5 \text{ V}, \text{ Induction}$ | ve Load                                      |          | 0    |       | J'.S |

|                      | t <sub>OFF</sub>    |                                        | (2nd Note 3)                                                                                        | VC LOAU                                      |          | 0.35 | . , , | μs   |

|                      | t <sub>C(OFF)</sub> |                                        |                                                                                                     |                                              |          | 0.10 | 1/2/  | μs   |

|                      | t <sub>rr</sub>     |                                        |                                                                                                     |                                              | <u> </u> | 0.10 | -     | μs   |

|                      | I <sub>CES</sub>    | Collector - Emitter Leakage            | V <sub>CE</sub> = V <sub>CES</sub>                                                                  |                                              | -0       |      | 1     | mA   |

|                      |                     | Current                                |                                                                                                     |                                              |          |      |       |      |

#### 2nd Notes:

#### **Control Part**

| Symbol                | Parameter                                  | Conditions                                                                                          | Min. | Тур. | Max. | Unit |

|-----------------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------|------|------|------|------|

| I <sub>QCCL</sub>     | Quiescent V <sub>C</sub> Jupply<br>Current | V = 15 V V <sub>CC(L)</sub> - COM                                                                   | -    | -    | 23   | mA   |

| Госсн                 | GU.                                        | V <sub>CC</sub> = 1; V<br>IN <sub>(UH, VH, VH)</sub> = 0 V<br>V <sub>CC(H)</sub> - ; ON             | -    | -    | 600  | μА   |

| I <sub>ORS</sub>      | Puiescent V Supply Trei                    | $V_{BS} = 15 \text{ V}$ $V_{S(U)}, V_{S(U)}, V_{B(V)} - V_{S(V)},$ $V_{B(W)} - V_{S(W)}$            | -    | -    | 500  | μА   |

| V <sub>FOH</sub>      | Fac Output Voitage                         | $V_{SC} = 0 \text{ V}, V_{TO} \text{ Circuit: } 4.7 \text{ k}\Omega \text{to } 5 \text{ V Pull-up}$ | 4.5  | -    | -    | V    |

| )L                    | CE CX                                      | V <sub>SC</sub> = 1 v, V <sub>FO</sub> Circuit: 4.7 kΩto 5 V Pull-up                                | -    | -    | 0.8  | V    |

| V <sub>SC, ref)</sub> | Shon Circuit Current<br>Trip Level         | V <sub>CC</sub> = 15 V (2nd Note 4)                                                                 | 0.45 | 0.50 | 0.55 | V    |

| TSD                   | Over-Temperature<br>Protection             | Temperature at LVIC                                                                                 | -    | 160  | -    | °C   |

| ΔTSD                  | Over-Temperature<br>Protection Hysterisis  | Temperature at LVIC                                                                                 | -    | 5    | -    | °C   |

| UV <sub>CCD</sub>     | Supply Circuit                             | Detection Level                                                                                     | 10.7 | 11.9 | 13.0 | V    |

| UV <sub>CCR</sub>     | Under-Voltage Protection                   | Reset Level                                                                                         | 11.2 | 12.4 | 13.4 | V    |

| UV <sub>BSD</sub>     |                                            | Detection Level                                                                                     | 10   | 11   | 12   | V    |

| UV <sub>BSR</sub>     |                                            | Reset Level                                                                                         | 10.5 | 11.5 | 12.5 | V    |

| t <sub>FOD</sub>      | Fault-Out Pulse Width                      | C <sub>FOD</sub> = 33 nF (2nd Note 5)                                                               | 1.0  | 1.8  | -    | ms   |

| V <sub>IN(ON)</sub>   | ON Threshold Voltage                       | Applied between $IN_{(UH)}$ , $IN_{(VH)}$ , $IN_{(WH)}$ , $IN_{(UL)}$ ,                             | 2.8  | -    | -    | V    |

| V <sub>IN(OFF)</sub>  | OFF Threshold Voltage                      | IN <sub>(VL)</sub> , IN <sub>(WL)</sub> - COM                                                       | -    | -    | 0.8  | V    |

gare switching time of IGET itself under the ว่าจากgate diving condition internally. 3.  $t_{ON}$  and  $t_{OFF}$  include the propagation delay time of the internal drive IC.  $t_{C(...)}$  ar. For the detailed information, please see Figure 4.

<sup>4.</sup> Short-circuit protection is functioning only at the low-sides.

<sup>5.</sup> The fault-out pulse width  $t_{FOD}$  depends on the capacitance value of  $C_{FOD}$  according to the following approximate equation:  $C_{FOD} = 18.3 \times 10^{-6} \times t_{FOD}$  [F]

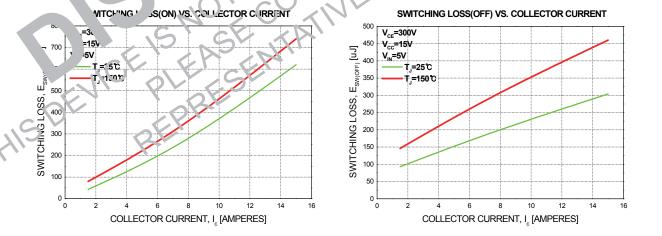

Figure 5. Switching Loss Characteristics (Typical)

#### **Bootstrap Diode Part**

| Symbol          | Parameter             | Conditions                                    | Min. | Тур. | Max. | Unit |

|-----------------|-----------------------|-----------------------------------------------|------|------|------|------|

| $V_{F}$         | Forward Voltage       | I <sub>F</sub> = 0.1 A, T <sub>C</sub> = 25°C | -    | 2.5  | -    | V    |

| t <sub>rr</sub> | Reverse Recovery Time | I <sub>F</sub> = 0.1 A, T <sub>C</sub> = 25°C | -    | 80   | -    | ns   |

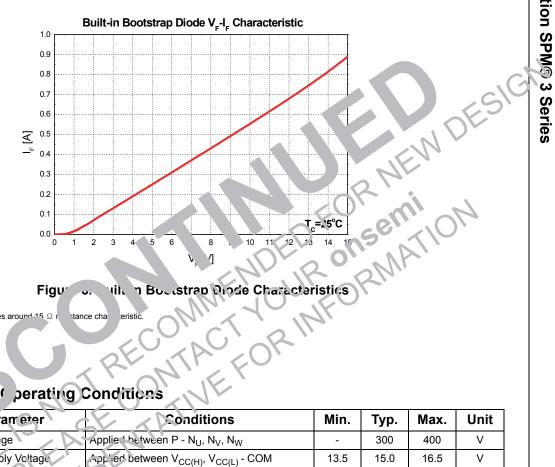

Figv'

#### 2nd Notes:

6. Built-in bootstrap diode includes around 15  $\Omega$  r

### Recominanced ( perating Conditions

| Ī | \mpr                                             | Param eter Param eter                  | Conditions                                                                                  | Min. | Тур. | Max. | Unit   |

|---|--------------------------------------------------|----------------------------------------|---------------------------------------------------------------------------------------------|------|------|------|--------|

|   | , SN                                             | Supply Voitage                         | Applied between P - N <sub>U</sub> , N <sub>V</sub> , N <sub>W</sub>                        | -    | 300  | 400  | V      |

|   |                                                  | Control Supply Voltage                 | Applied between $V_{CC(H)}$ , $V_{CC(L)}$ - COM                                             | 13.5 | 15.0 | 16.5 | V      |

|   | V <sub>BS</sub>                                  | r.liqh-Side Bias Voltage               | Applied between $V_{B(U)}$ - $V_{S(U)}$ , $V_{B(V)}$ - $V_{S(V)}$ , $V_{B(W)}$ - $V_{S(W)}$ | 13.0 | 15.0 | 18.5 | V      |

|   | aV <sub>CC</sub> ./ at,<br>dV <sub>BS</sub> / dt | Control Supply Varia ion               |                                                                                             | -1   | ı    | 1    | V / μs |

|   | t <sub>dead</sub>                                | Blanking Time for Preventing Arm-Short | Each Input Signal                                                                           | 2    | -    | -    | μs     |

|   | $f_{PWM}$                                        | PWM Input Signal                       | $-40^{\circ}C \leq  T_{C} \leq 125^{\circ}C, -40^{\circ}C \leq  T_{J} \leq  150^{\circ}C$   | -    | 1    | 20   | kHz    |

|   | $V_{SEN}$                                        | Voltage for Current Sensing            | Applied between $N_U$ , $N_V$ , $N_W$ - COM (Including Surge Voltage)                       | -4   |      | 4    | V      |

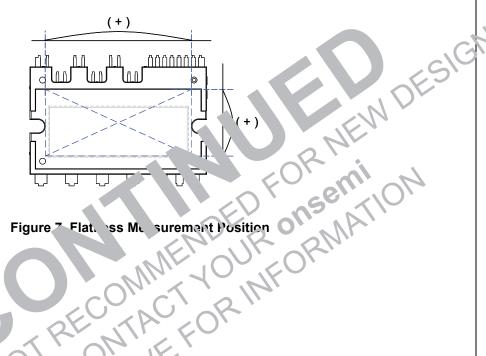

### **Mechanical Characteristics and Ratings**

| Parameter       | Соі                | Min.                 | Тур. | Max.  | Unit |     |

|-----------------|--------------------|----------------------|------|-------|------|-----|

| Mounting Torque | Mounting Screw: M3 | Recommended 0.62 N•m | 0.51 | 0.62  | 0.80 | N•m |

| Device Flatness |                    | See Figure 7         | 0    | -     | +120 | μm  |

| Weight          |                    |                      | -    | 15.00 | -    | g   |

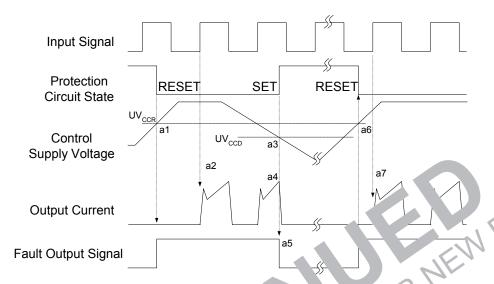

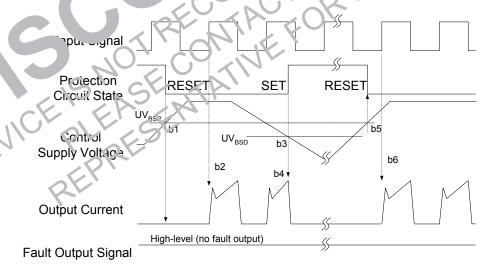

#### **Time Charts of Protective Function**

- a1 : Control supply voltage rises: after the voltage rises UV<sub>CCR</sub>, the circuit and erate when next input is applied.

- a2: Normal operation: IGBT ON and carrying current.

- a3 : Under-voltage detection (UV<sub>CCD</sub>).

- a4: IGBT OFF in spite of control input condition.

- a5 : Fault output operation starts.

- a6 : Under-voltage reset (UV<sub>CCR</sub>).

- a7 : Normal operation: IGBT ON and c rying c ren.

Figure 8. Inder-Voltage Protection (Low Side)

- b1 : Control supply voltage rises: after the voltage reaches UV<sub>BSR</sub>, the circuits start to operate when next input is applied.

- b2: Normal operation: IGBT ON and carrying current.

- b3 : Under-voltage detection (UV<sub>BSD</sub>).

- b4: IGBT OFF in spite of control input condition, but there is no fault output signal.

- b5: Under-voltage reset (UV<sub>BSR</sub>).

- b6: Normal operation: IGBT ON and carrying current.

Figure 9. Under-Voltage Protection (High-Side)

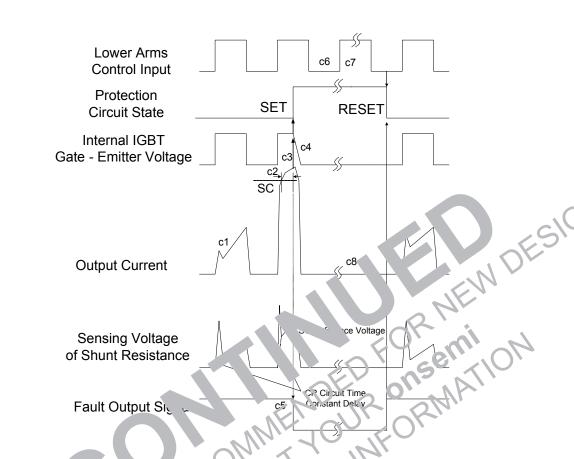

(with the external shunt residence and

- c1: Normal operation: IGB ON and arrying current

- c2 : Short-circuit arent dete in (5 trigger)

- c3 : Hard ICRT

- c4 : ICPT tun. OFF

- Fault thu mer operation starts: the pulse width of the fault output signal is set by the external capacitor  $C_{FO}$ .

- ct 'nput "L W": GBT OFF state.

- c7: ... "IGH": 'GB' CN state, but ouring the active period of fault output, the IGBT doesn't turn ON.

- c8: IGكT OFF state.

Figure 10 Short-Circuit Protection (Low-Side Operation Only)

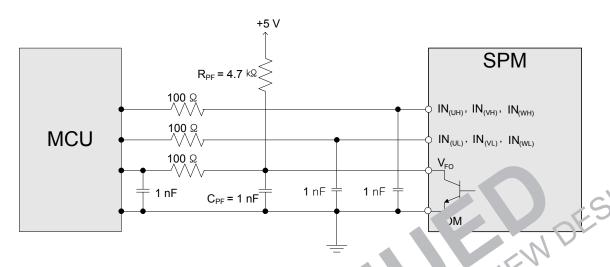

Figure 11. Recommended MCU I/O In arfa a Ci suit

#### 3rd Notes:

- RC coupling at each input might change depending on the PWM control scheme in the au signal section of the Motion SPM<sup>®</sup> 3 product integrates a 5 kΩ (typ.) pull-down results.

The logic input works with standard CMOS or LSTTL outputs.

## These values depend on PWM control algorithm

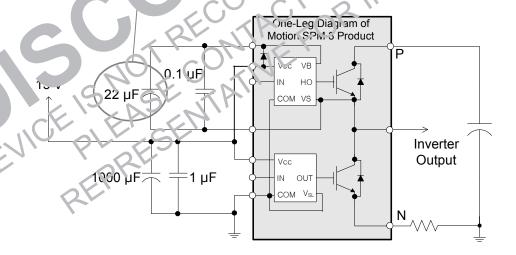

Figure 12. Recommended Bootstrap Operation Circuit and Parameters

3. The ceramic capacitor placed between  $V_{CC}$  - COM should be over 1  $\mu$ F and mounted as close to the pins of the Motion SPM 3 product as possible.

#### Figure 13. Typical Application Circuit

#### 4th M

the wiring of each input should he as snort as possible (was than 2 - 3cm). avoid r

- gratii y an application execific type of riVI C inside the Mohor SPM® 3 product, direct coupling to MCU terminals without any optocoupler or transformer isolavirtue of tı 3 possi<sup>t</sup>

- γρε. This sign a line should be called up to the positive side of the 5 V power supply with approximately 4.7 kΩresistance (please refer to Fig-3. V<sub>FO</sub> open-cc lector

- 4.  $C_{SP15}$  of around  $\kappa$  ven times large, than bootstrap  $\kappa$  pactor  $C_{BS}$  is recommended.

- 5. V<sub>FO</sub> couput oulse width should be determined by conflecting an external capacitor (C<sub>FOD</sub>) between C<sub>FOD</sub> (pin 7) and COM (pin 2). (Example: if C<sub>FOD</sub> = 33 nF, then t<sub>FO</sub> = 1.8 ms (typ.,) Ple ase refer to the 2nd note 5 for calculation method.

- 6. Input signal is active-HIGH type. There is  $\epsilon$ . 5 kΩ resistor inside the IC to pull down each input signal line to GND. RC coupling circuits should be used to prevent input signal oscillation.  $R_S C_{PS}$  time constants in solud be selected in the range 50 ~ 150 ns.  $C_{PS}$  should not be less than 1 nF (recommended  $R_S = 100 \ \Omega$ ,  $C_{PS} = 1 \ nF$ ).

- 7. To prevent errors of the protection function, the wiring around R<sub>F</sub> and C<sub>SC</sub> should be as short as possible.

- 8. In the short-circuit protection circuit, please select the  $R_FC_{SC}$  time constant in the range 1.5 ~ 2.0  $\mu s$ .

- 9. Each capacitor should be mounted as close to the pins of the Motion SPM 3 product as possible.

- 10. To prevent surge destruction, the wiring between the smoothing capacitor and the P & GND pins should be as short as possible. The use of a high-frequency non-inductive capacitor of around 0.1  $\sim$  0.22  $\mu F$  between the P & GND pins is recommended.

- 11. Relays are used in almost every systems of electrical equipment in home appliances. In these cases, there should be sufficient distance between the MCU and the relays.

- 12.  $C_{SPC15}$  should be over 1  $\mu F$  and mounted as close to the pins of the Motion SPM 3 product as possible.

ON Semiconductor and III) are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns me rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="https://www.onsemi.com/site/pdt/Patent-Marking.pdf">www.onsemi.com/site/pdt/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.

Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that ON Semiconductor was negligent regarding the design or manufacture of the part. ON Semiconductor is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada

Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81-3-5817-1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative